The Impact of Temperature on Chip Radiation Tolerance

Project PI

Dr. Selahattin Sayil, Professor, Phillip M. Drayer Department of Electrical Engineering

Short Description

Circuit sensitivity to radiation is continuously increasing as transistors are getting smaller and operating at lower voltages. On the other hand, heat generation in microchip circuits has increased rapidly due to same scaling trends. As industry tries to address radiation sensitivity, they need to be aware of the impact of temperature increases on radiation tolerance. This project aims to study the effect of temperature on various radiation mechanisms such as radiation induced glitches, delay and coupling effects and compensate the thermal effects.

Full Description

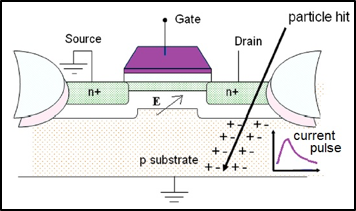

For commercial chips at ground level, radiation effects occur due to atmospheric neutrons or alpha particles emitted from radioactive decay of uranium and thorium impurities within the chip packaging.

Scaling of semiconductor technologies has created concern that newer generations of commercial microchips (ICs) will exhibit unacceptable levels of reliability due to radiation induced transients. Soft error rates are a strong function of transient pulse widths that greatly depend on temperature. Hence, an increase in SET pulse width (due to increasing temperature) may negate the mitigation efforts and increase error rates. This project aims to compensate for thermally induced soft error effects using a temperature sensor and a novel compensation method. By identifying the impact of of thermal effects, design principles will also be developed for other radiation hardening methodologies currently being used in industry, avionics and military applications.

Funding

The project is funded by Lamar Research Enhancement Grant

Publications

- Sayil, S., Soft Error Mechanisms, Modeling and Mitigation, Publisher: Springer, New York, NY, 2016.

- Sayil, S., Shah, A.H. , Zaman, ma, Islam, ma,"Soft Error Mitigation using Transmission Gate with varying Gate and Body Bias", IEEE Design & Test, Vol. 34, No: 1, pp. 47-56 , 2017.